# **LED Driver**

# W2RG012RN

# **OMRON**

#### **■** Features

#### **Optimal IC for LED performance control**

- The built-in exponential PWM gradation control function with up to 256 levels enables visually pleasing fade-ins and fade-outs.

- Capable of dynamically driving matrix-connected LEDs and individually controlling up to 128 channels.

- Serial bus connection allows up to 15 of these ICs to be connected on the same communication line.

- 24 constant current outputs are housed in a compact package with 7 x 7 mm dimensions.

- Built-in thermal shutdown

# ■ Model Number Legend

**W2R G012RN**

(1) IC

(1) (2)

(2) Series name

# ■ Absolute Maximum Ratings

| Item                          | Symbol | Rating                  | Unit | Target terminals                                   |

|-------------------------------|--------|-------------------------|------|----------------------------------------------------|

| Power supply voltage          | VDD    | -0.3 to 7.0             | V    | VDD                                                |

| Input voltage                 | VIN    | -0.3 to VDD + 0.3 ≤ 7.0 | V    | SDA, SCL, RST, CE, ADR1, ADR0, DIV, COM            |

| Signal output voltage         | VSOUT  | -0.3 to VDD + 0.3 ≤ 7.0 | V    | SDO, OUTDC                                         |

| Drive output voltage          | VDOUT  | -0.3 to 20              | V    | OUTOR to 7R, OUTOG to 7G, OUTOB to 7B, OUTS0 to S3 |

| Drive output current/pin      | IDOUT  | 80 (*1)                 | mA   | OUTOR to 7R, OUTOG to 7G, OUTOB to 7B              |

| Switching output current/pin  | IDOUTS | 20                      | mA   | OUTS0 to S3                                        |

| Allowable loss                | Pd1    | 3.43 (*2)               | W    | -                                                  |

|                               | Pd2    | 1.80 (*2)               | W    | -                                                  |

|                               | Pd3    | 1.16 (*2)               | W    | -                                                  |

| Operating ambient temperature | Topr   | -20 to 85               | °C   | -                                                  |

| Storage ambient temperature   | Tstg   | -40 to 150              | °C   | -                                                  |

<sup>\*1.</sup> Consider the power consumption and allowable loss before use.

Pd1: Rtd = 27.4 mW/°C for a double-sided board with a copper foil area of 4900 mm² on the backside.

Pd2: Rtd = 14.4 mW/°C for a double-sided board with a copper foil area of 225 mm² on the backside.

Pd3: Rtd = 9.28 mW/°C for a single-sided board with a copper foil area of 36 mm<sup>2</sup>.

#### ■ Recommended Operating Conditions

| Item                          | Symbol | Rating     | Unit | Target terminals                        |

|-------------------------------|--------|------------|------|-----------------------------------------|

| Power supply voltage          | VDD    | 3.0 to 5.5 | V    | VDD                                     |

| Input voltage                 | VIN    | 0 to VDD   | V    | SDA, SCL, RST, CE, ADR1, ADR0, DIV, COM |

| Signal output current         | ISOUT  | -10 to 10  | mA   | SDO, OUTDC                              |

| Communication clock frequency | fSCL   | Max.5 (*1) | MHz  | SCL                                     |

<sup>\*1.</sup> Consider the timing characteristics before use.

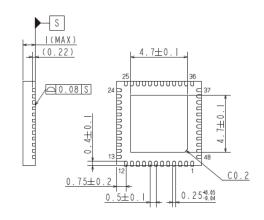

#### External Dimensions

[Unit: mm]

<sup>\*2.</sup> Values when a standard board (70 mm x 70 mm x 1.6 mmt, FR-4) is mounted. When used at a temperature of Ta=25°C or higher, reduce by the temperature derating factor Rtd [mW/°C].

# **■ Electrical Characteristics**

# (1) DC characteristics

$(Ta = 25^{\circ}C, VDD = 5V)$

| Item                                      | Symbol                           | Conditions                     | Sta       | andard valu | ies       | Unit                  | Target terminals             |  |

|-------------------------------------------|----------------------------------|--------------------------------|-----------|-------------|-----------|-----------------------|------------------------------|--|

| item                                      | Symbol Conditions                |                                | Min.      | Typ.        | Max.      | Offic                 | raiget terriiriais           |  |

| High level input voltage                  | VIH                              | -                              | VDD × 0.7 | ı           | -         | V                     | SDA, SCL, RST, CE            |  |

| Low level input voltage                   | VIL                              | -                              | -         | ı           | VDD × 0.3 | V                     | SDA, SCL, RST, CE            |  |

|                                           | VAD1                             | "10" output                    | VDD × 0.9 | -           | VDD + 0.3 | V                     |                              |  |

| A/D input voltage                         | VAD2                             | "11" output                    | VDD × 0.6 | -           | VDD × 0.7 | V                     | ADR1, ADR0,                  |  |

| AD input voitage                          | VAD3                             | "01" output                    | VDD × 0.3 | 1           | VDD × 0.4 | VDD × 0.4 $V$ DIV, CO |                              |  |

| VAD4                                      |                                  | "00" output                    | -0.3      | 1           | VDD × 0.1 | V                     | 1                            |  |

| High level signal output voltage          | VSOH                             | ISOUT = -5 mA                  | VDD - 0.5 | ı           | -         | V                     | CDC OUTDC                    |  |

| Low level signal output voltage           | VSOL                             | ISOUT = 5 mA                   | -         | •           | 0.5       | V                     | SDO, OUTDC                   |  |

| On-resistance 1                           | RON1                             | -                              | -         | 6.3         | 10        | Ω                     |                              |  |

| Pin-to-pin current accuracy               | Pin-to-pin current accuracy Δ IP |                                | -3        | 1           | +3        | %                     | OUTOR to 7R,                 |  |

| Inter-device current accuracy $\Delta$ ID |                                  | IDOUT = 20 mA                  | -6        | 1           | +6        | %                     | OUT0G to 7G,<br>OUT0B to 7B, |  |

| Drive output leakage current              | IDL                              | -                              | -         | -           | 1         | μΑ                    | 001001070,                   |  |

| On-resistance 2                           | RON2                             | -                              |           |             | 20        | Ω                     | OUTS0 to S3                  |  |

| Current consumption during operation      | IDD                              | Total output:<br>IDOUT = 20 mA | -         | 5.0         | 7.0       | mA                    | VDD                          |  |

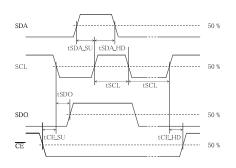

# (2) Timing characteristics

# (2)-1 Addressed serial communication

$(Ta = -20 \text{ to } 85^{\circ}\text{C}, VDD = 3.0 \text{ to } 5.5\text{V})$

| Item                            | Symbol Conditions |                         | Standard values |      |      | Unit  | Target terminals |

|---------------------------------|-------------------|-------------------------|-----------------|------|------|-------|------------------|

| item                            | Syllibol          | Conditions              | Min.            | Тур. | Max. | Offic | Target terminals |

| Communication clock pulse width | tSCL              | -                       | 100             | -    | -    | ns    | SCL              |

| Data setup time                 | tSDA_SU           | -                       | 90              | -    | -    | ns    | CCI CDA          |

| Data hold time                  | tSDA_HD           | -                       | 90              | -    | -    | ns    | SCL, SDA         |

| CE setup time                   | tCE_SU            | -                       | 50              | -    | -    | ns    | SCL, SDA, CE     |

| CE hold time                    | tCE_HD            | -                       | 50              | -    | -    | ns    | SUL, SDA, UE     |

| Data output time                | tSDO              | Load capacitance 100 pF | -               | -    | 80   | ns    | SCL, SDO         |

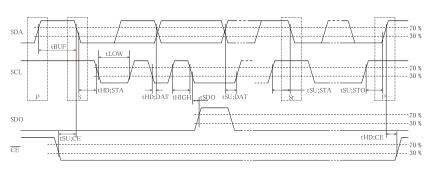

# (2)-2 I2C-compliant serial communication

$(Ta = -20 \text{ to } 85^{\circ}\text{C}, VDD = 3.0 \text{ to } 5.5\text{V})$

| Chambers values  |         |                         |                 |      |      | ,     |                  |

|------------------|---------|-------------------------|-----------------|------|------|-------|------------------|

| Item             | Symbol  | Conditions              | Standard values |      |      | Unit  | Target terminals |

| item             | Cymbol  | Odriditiono             | Min.            | Тур. | Max. | O.I.C | rarget terrimale |

| Clock "L" period | tLOW    | -                       | 50              | -    | -    | ns    | SCL              |

| Clock "H" period | tHIGH   | -                       | 50              | -    | -    | ns    | SCL              |

| Bus release time | tBUF    | -                       | 80              | ı    | -    | ns    | SDA              |

| Start setup time | tSU;STA | -                       | 50              | -    | -    | ns    |                  |

| Start hold time  | tHD;STA | -                       | 50              | -    | -    | ns    |                  |

| Stop setup time  | tSU;STO | -                       | 50              | -    | -    | ns    | SCL, SDA         |

| Data setup time  | tSU;DAT | -                       | 30              | -    | -    | ns    |                  |

| Data hold time   | tHD;DAT | -                       | 0               | -    | -    | ns    |                  |

| CE setup time    | tSU;CE  | -                       | 50              | -    | -    | ns    | SCL, SDA, CE     |

| CE hold time     | tHD;CE  | -                       | 50              | -    | -    | ns    | JOL, JDA, GE     |

| Data output time | tSDO    | Load capacitance 100 pF | -               | -    | 80   | ns    | SCL, SDO         |

Addressed serial communication

I2C-compliant serial communication

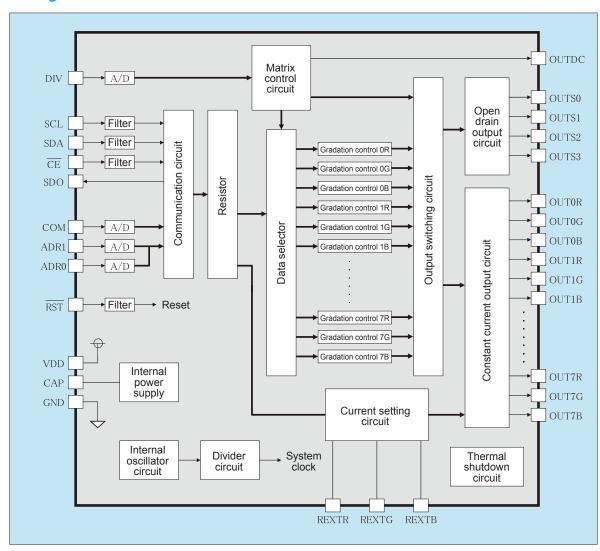

# **■** Function Overview

24 channels of LEDs are driven by constant current or constant voltage.

Furthermore, dynamic lighting (pulsed lighting) of LEDs connected in a matrix can be performed. During dynamic lighting, the LEDs of 48 channels (2-segment), 96 channels (4-segment), and 128 channels (8-segment) can be individually gradation-controlled.

#### (1) Command reception

The LED lighting command is received via serial communication. In terms of communication methods, three types of addressed serial communication and I2C-compliant serial communication are supported. Up to 128 LED lighting data can be sent continuously. The start signal and device address only need to be specified once, thus reducing the overall communication volume.

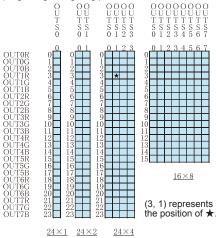

#### (2) Gradation control

256 gradation levels can be illuminated. Each gradation level is assigned to a duty ratio according to an exponential function, allowing expression that corresponds to the characteristics of human vision.

#### (3) Matrix control

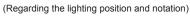

It supports matrix connections of 24 x 1, 24 x 2, 24 x 4, and 16 x 8.

By controlling the switching timing of dynamic lighting, accidental lighting during switching can be prevented.

#### (4) Power-saving control

Drives the power consumption during LED lighting at 75%/50%/25% of the normal operating power. Batch switching is possible using communication commands, making it easy to switch between normal and power-saving modes.

The control method can be selected between current control and duty ratio control.

Current control switches the output current to 75%, 50%, or 25% based on the current set at the current setting terminals REXTR/REXTG/REXTB. Duty ratio control switches the output duty ratio to 75%, 50%, or 25% based on the gradation-specified duty ratio.

#### (5) Number of control channels

Up to 15 devices can be connected by specifying the address. This allows for the control of up to 1920 channels of LEDs. In addition, more devices can be connected by switching CE terminals.

#### **■ Block Diagram**

#### **■ Terminal List**

| No. | Terminal name | Terminal description       | I/O | Function                         |

|-----|---------------|----------------------------|-----|----------------------------------|

| 1   | SDA           | Serial data input          | I   | CMOS, Filter                     |

| 2   | SCL           | Serial clock input         | I   | CMOS, Filter                     |

| 3   | CE            | Chip enable input (*1)     | I   | CMOS, Filter                     |

| 4   | VDD           | Power supply               | Р   |                                  |

| 5   | CAP           | Capacitor (*2)             |     |                                  |

| 6   | GND           | Ground                     | Р   |                                  |

| 7   | ADR1          | Device address 1           | I   | Resistance voltage divider input |

| 8   | ADR0          | Device address 0           | I   | Resistance voltage divider input |

| 9   | DIV           | Division mode              | I   | Resistance voltage divider input |

| 10  | COM           | Communication mode         | I   | Resistance voltage divider input |

| 11  | REXTR         | Current setting resistor R |     |                                  |

| 12  | REXTG         | Current setting resistor G |     |                                  |

| 13  | REXTB         | Current setting resistor B |     |                                  |

| 14  | OUT0R         | Output 0R                  | 0   | Constant current                 |

| 15  | OUT0G         | Output 0G                  | 0   | Constant current                 |

| 16  | OUT0B         | Output 0B                  | 0   | Constant current                 |

| 17  | GND           | Ground                     | Р   |                                  |

| 18  | OUT1R         | Output 1R                  | 0   | Constant current                 |

| 19  | OUT1G         | Output 1G                  | 0   | Constant current                 |

| 20  | OUT1B         | Output 1B                  | 0   | Constant current                 |

| 21  | OUT2R         | Output 2R                  | 0   | Constant current                 |

| 22  | OUT2G         | Output 2G                  | 0   | Constant current                 |

| 23  | GND           | Ground                     | Р   |                                  |

| 24  | OUT2B         | Output 2B                  | 0   | Constant current                 |

| No. | Terminal name | Terminal description           | I/O | Function              |

|-----|---------------|--------------------------------|-----|-----------------------|

| 25  | OUT3R         | Output 3R                      | 0   | Constant current      |

| 26  | OUT3G         | Output 3G                      | 0   | Constant current      |

| 27  | OUT3B         | Output 3B                      | 0   | Constant current      |

| 28  | OUT4R         | Output 4R                      | 0   | Constant current      |

| 29  | OUT4G         | Output 4G                      | 0   | Constant current      |

| 30  | OUT4B         | Output 4B                      | 0   | Constant current      |

| 31  | GND           | Ground                         | Р   |                       |

| 32  | OUT5R         | Output 5R                      | Ο   | Constant current      |

| 33  | OUT5G         | Output 5G                      | 0   | Constant current      |

| 34  | OUT5B         | Output 5B                      | 0   | Constant current      |

| 35  | OUT6R         | Output 6R                      | 0   | Constant current      |

| 36  | OUT6G         | Output 6G                      | 0   | Constant current      |

| 37  | GND           | Ground                         | Р   |                       |

| 38  | OUT6B         | Output 6B/Output switching 4   | О   | Constant current      |

| 39  | OUT7R         | Output 7R/Output switching 5   | О   | Constant current      |

| 40  | OUT7G         | Output 7G/Output switching 6   | О   | Constant current      |

| 41  | OUT7B         | Output 7B/Output switching 7   | Ο   | Constant current      |

| 42  | OUTS0         | Output switching 0             | О   | N-ch open drain       |

| 43  | OUTS1         | Output switching 1             | 0   | N-ch open drain       |

| 44  | OUTS2         | Output switching 2             | О   | N-ch open drain       |

| 45  | OUTS3         | Output switching 3             | О   | N-ch open drain       |

| 46  | OUTDC         | Synchronization control output | О   | CMOS                  |

| 47  | SDO           | Serial data output             | 0   | CMOS                  |

| 48  | RST           | Reset (*3)                     | I   | CMOS, Filter, Pull-up |

<sup>\*1.</sup> If the CE terminal is not used, set it to low (L). (Excluding CE-D8 mode)

# ■ Terminal Description

## (1) ADR terminal

Set the device address by inputting the resistance voltage divider. Table 1 shows the correspondence between device addresses and ADR pin voltages.

#### (2) DIV terminal

Set the matrix configuration of the LEDs to be connected by inputting the DIV terminal resistance voltage divider.

Table 2 shows the correspondence between matrix configurations and DIV terminal voltages, and Table 3 shows the correspondence between matrix configurations and terminal functions.

(3) COM terminal

Set the communication mode by inputting the the resistance voltage divider. Table 4 shows the correspondence between communication modes and COM pin voltages.

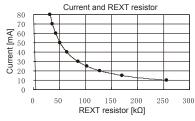

#### (4) REXT terminal

The current is set by connecting to GND via an external REXT resistor. Table 5 shows the current vs. REXT resistor.

#### (5) RST terminal

When the input is "L", each buffer is in the initial state, the constant-current output terminal and the open-drain output terminal are in open outputs, and the CMOS output terminal is in "L" output.

Table 1: Device address and ADR terminal voltage

| terminai voitage |                  |                  |  |  |

|------------------|------------------|------------------|--|--|

| Device address   | ADR1             | ADR0             |  |  |

| 0000             | GND              | GND              |  |  |

| 0001             | GND              | VDD×1/3          |  |  |

| 0010             | GND              | VDD              |  |  |

| 0011             | GND              | $VDD \times 2/3$ |  |  |

| 0100             | $VDD \times 1/3$ | GND              |  |  |

| 0101             | VDD×1/3          | VDD×1/3          |  |  |

| 0110             | VDD×1/3          | VDD              |  |  |

| 0111             | VDD×1/3          | $VDD \times 2/3$ |  |  |

| 1000             | VDD              | GND              |  |  |

| 1001             | VDD              | VDD×1/3          |  |  |

| 1010             | VDD              | VDD              |  |  |

| 1011             | VDD              | $VDD \times 2/3$ |  |  |

| 1100             | $VDD \times 2/3$ | GND              |  |  |

| 1101             | $VDD \times 2/3$ | $VDD \times 1/3$ |  |  |

| 1110             | $VDD \times 2/3$ | VDD              |  |  |

| 1111 (reserve)   | $VDD \times 2/3$ | $VDD \times 2/3$ |  |  |

Table 2: Matrix configuration and DIV terminal voltage

| •                    |         |  |  |

|----------------------|---------|--|--|

| Matrix configuration | DIV     |  |  |

| 24×1                 | GND     |  |  |

| 24×2                 | VDD×1/3 |  |  |

| $24 \times 4$        | VDD     |  |  |

| 16×8                 | VDD×2/3 |  |  |

Table 3: Matrix configuration and terminal voltage

| Output   |             | Matrix cor     | nfiguration |            |  |  |

|----------|-------------|----------------|-------------|------------|--|--|

| terminal | 24×1        | 24×2           | 24×4        | 16×8       |  |  |

| OUT0R    |             | OU'            |             | •          |  |  |

| OUT0G    |             | OU'            | T0G         |            |  |  |

| OUT0B    |             | OU'            | T0B         |            |  |  |

| OUT1R    |             | OU'            | T1R         |            |  |  |

| OUT1G    |             | OU'            | T1G         |            |  |  |

| OUT1B    |             | OU'            |             |            |  |  |

| OUT2R    |             | OU'            | T2R         |            |  |  |

| OUT2G    |             | OU'            |             |            |  |  |

| OUT2B    |             | OU'            |             |            |  |  |

| OUT3R    |             | OU.            |             |            |  |  |

| OUT3G    |             | OUT3G          |             |            |  |  |

| OUT3B    | OUT3B       |                |             |            |  |  |

| OUT4R    | OUT4R       |                |             |            |  |  |

| OUT4G    | OUT4G       |                |             |            |  |  |

| OUT4B    | OUT4B       |                |             |            |  |  |

| OUT5R    | OUT5R       |                |             |            |  |  |

| OUT5G    |             | OUT5G (Not use |             |            |  |  |

| OUT5B    |             | OUT5B          |             | (Not used) |  |  |

| OUT6R    |             | OUT6R          |             | (Not used) |  |  |

| OUT6G    |             | OUT6G          |             | (Not used) |  |  |

| OUT6B    |             | OUT6B OUTS4    |             |            |  |  |

| OUT7R    | OUT7R OUTS5 |                |             |            |  |  |

| OUT7G    | OUT7G OUTS6 |                |             |            |  |  |

| OUT7B    | OUT7B OUTS7 |                |             |            |  |  |

| OUTS0    | OUTS0       |                |             |            |  |  |

| OUTS1    | (Not used)  |                | OUTS1       |            |  |  |

| OUTS2    |             | (Not used)     |             | TS2        |  |  |

| OUTS3    | (Not used)  | (Not used)     | OU          | TS3        |  |  |

Table 4 shows the correspondence between communication modes and COM pin voltages.

| Communication mode                       | COM     |

|------------------------------------------|---------|

| Addressed serial communication (SP-D8)   | GND     |

| Addressed serial communication (SP-D7)   | VDD×1/3 |

| I2C-compliant serial communication (I2C) | VDD     |

| Addressed serial communication (CE-D8)   | VDD×2/3 |

Table 5: Current and the REXT resistor

| Current | REXT resistor |

|---------|---------------|

| [mA]    | [kΩ]          |

| 10      | 256           |

| 15      | 171           |

| 20      | 128           |

| 25      | 102           |

| 30      | 85.3          |

| 40      | 64.0          |

| 50      | 51.2          |

| 60      | 42.7          |

| 70      | 36.6          |

| 80      | 32.0          |

(Current setting method)

IDOUT [mA] = 2560/RÉXT resistor [k $\Omega$ ]

(Recommended operating range)

IDOUT: 10 to 80 mA (Instantaneous value) \*1. The effective value is IDOUT/division factor.

<sup>\*2.</sup> The CAP terminal connects a power supply smoothing capacitor. Connect a 0.1 µF capacitor between the CAP terminal and GND.

<sup>\*3.</sup> The RST terminal has a built-in 100 kΩ pull-up resistor. If not used, we recommend connecting a 0.1 uF capacitor between the RST terminal and GND for stable operation.

<sup>\*4.</sup> Put unused output terminals in the open state.

# **■ Communication Specifications**

This IC supports four communication methods. Set at the communication mode setting terminal (COM).

(1) Addressed serial communication method (SP-D8 mode)

Word length 0: 8-bit gradation data specification

| bit<br>SCL  | 1 2 3 4 5 6 7 8 9 | 10 11 12 13 14 15 16 17 18        | 19       | 20 21 22 23 24 25 26 27                                 | 28<br><b>f</b> | 29 30 31 32 33 34 35 36            |        | 884 885 886 887 888 889 890 891      | 892 893     | 894 895 896                 |

|-------------|-------------------|-----------------------------------|----------|---------------------------------------------------------|----------------|------------------------------------|--------|--------------------------------------|-------------|-----------------------------|

| SDA<br>Name | START             | Device   Device   R   address   W | S<br>P   | Resistor address  Resistor selection data  reg_dat[7:0] | S<br>P         | Gradation data (0) light_dat0[7:0] | 0<br>P | Gradation data (95) light_dat95[7:0] | 1 1<br>STOP | 1 1 1<br>Byte<br>adjustment |

| SDO<br>Name | 0                 | 0                                 | 1<br>ACK | 0                                                       | 1<br>ACK       | 0                                  | ACK    | 0                                    | 1 0<br>ACK  | 0                           |

<sup>\*</sup> Word length

Word length 1: 4-bit gradation data specification

|    | o. a o g                                | ,   |                       |    | 1  |          |             |    |             |     |             |             |     |     |              |             |     |     |     |     |        |    |

|----|-----------------------------------------|-----|-----------------------|----|----|----------|-------------|----|-------------|-----|-------------|-------------|-----|-----|--------------|-------------|-----|-----|-----|-----|--------|----|

| 20 | 21 22 23 24 25 26 27                    | 28  | 29 30 31              | 32 | 33 | 34       | 35          | 36 | 1           | 452 | 453         | 454         | 455 | 456 | 457          | 458         | 459 | 460 | 461 | 462 | 463 4  | 64 |

| £  |                                         | ۲   | <u> </u>              | ſ  | Ţ  | $\Gamma$ | ſ           | Ţ  | À           | £   | Ъ           | Ь           | Ь   | Ь   | Ŀ            | Ъ           | £   | f   | £   | Ţ   | Ĺ      | Ì  |

| 1  |                                         | 0   |                       |    |    |          |             |    | 0           |     |             |             |     |     |              |             |     | 1   | 1   | 1   | 1      | 1  |

| *  | Resistor address                        | S   | Gradation<br>data (0) |    | C  | lata     | atio        |    |             | d   | rad<br>lata | (94         | )   | C   | irad<br>lata | (95         | 5)  | ST  | ΩĐ  |     | Byte   |    |

| F  | Resistor selection data<br>reg_dat[7:0] | Р   | light_dat(<br>[3:0]   | )  | li |          | _dat<br>:0] | 1  | P           | li  | ght_<br>[3  | dat!<br>:0] | 94  | li. | ght_<br>[3   | dat!<br>:0] | 95  | 31  | OF  | adj | ustmer | ١t |

|    | 0                                       | 1   |                       | (  | )  |          |             |    | 1           |     |             |             | (   | )   |              |             |     | 1   | 0   |     | 0      | _  |

|    |                                         | ACK |                       |    |    |          |             |    | Ad <b>\</b> |     |             |             |     |     |              |             |     | ACK |     | :   |        | Ξ  |

Byte adjustment: When sending data in 8-bit units, specify "1" for the remainder pit after STOP.

#### (2) Addressed serial communication method (SP-D7 mode)

| bit<br>SCL | 1 2 3 4 5 6 7 8<br><b>f f f f f</b> f f | 9 10 11 12 13 14 15 16                | 17 18 | 19 20 21 22 23 24<br><b>f f f f f</b>  | 25<br>• | 26 27 28 29 30 31 32<br>f f f f f f f |    |                     | 793 794 795 796 797 798 799 800 |

|------------|-----------------------------------------|---------------------------------------|-------|----------------------------------------|---------|---------------------------------------|----|---------------------|---------------------------------|

| SDA        | 1 1 1 1 1 1 1 1                         | 0 0 1 0                               | 0     |                                        | 0       |                                       | 0  |                     | 1 1 1 1 1 1 1 1                 |

| Name       | START                                   | Device Device address                 | 3     | Resistor address                       | S       | Gradation data (0)                    |    | Gradation data (95) | STOP                            |

| IVallic    | STAKI                                   | Device selection data<br>dvc_dat[6:0] | P Re  | esistor selection data<br>reg_dat[6:0] | Р       | light_dat0[6:0]                       | P  | light_dat95[6:0]    | 5101                            |

| SDO        | 0                                       | 0                                     | 1     | 0                                      | 1       | 0                                     | M/ | 0                   | 1 0                             |

| Name       |                                         |                                       | ACK   |                                        | ACK     |                                       | Αď |                     | ACK                             |

#### (3) Addressed serial communication method (CE-D8 mode)

Word length 0: 8-bit gradation data specification

| bit      |       | 1 | 2          | 3 | 4            | 5                      | 6 | 7    | 8      | 9     | 10   | 11  | 12    | 13            | 14   | 15   | 16  | 17     | 18 | 19   | 20    | 21   | 22   | 23 | 24  | 777      | 778 | 779   | 780  | 781  | 782 | 783 | 784 |      |

|----------|-------|---|------------|---|--------------|------------------------|---|------|--------|-------|------|-----|-------|---------------|------|------|-----|--------|----|------|-------|------|------|----|-----|----------|-----|-------|------|------|-----|-----|-----|------|

| CE       | ļ     | Ш |            |   |              |                        |   | П    |        | П     |      | П   |       |               |      |      |     | $\Box$ |    |      |       |      |      |    |     | $\Gamma$ |     | П     |      |      |     | П   |     |      |

| SCL      |       | ſ | ſ          | ſ | ſ            | ſ                      | ſ | ſ    | £      | Ŧ     | ſ    | ſ   | ſ     | ſ             | ſ    | ſ    | ſ   | ı      | J  | ſ    | ſ     | £    | ſ    | ſ  | 1   | N-       | ſ   | ſ     | ſ    | ſ    | £   | ſ   | ſ   |      |

| SDA      | 1     | 0 | 1          | 0 |              |                        |   |      | 0      | 0     |      |     |       |               |      |      |     |        |    |      |       |      |      |    |     | )):]     |     |       |      |      |     |     |     | 1    |

| Name     | START | D | evic<br>ID | е |              | De <sup>v</sup><br>add |   |      | R<br>W | *     |      | Res | sisto | or a          | ddre | ess  |     |        |    |      | atior |      |      |    |     | /        |     |       |      | n da |     |     |     | STOP |

| Name     | SIARI | [ | Dev        |   | sele<br>c_da |                        |   | lata |        | F     | Resi |     |       | lect<br>it[7: |      | data | а   |        |    | ligh | t_da  | t0[′ | 7:0] |    | (   |          | ]   | light | t_da | t95  | 7:0 | ]   |     | 3101 |

| SDO      | 0     |   |            |   | 0            |                        |   |      | 1      |       |      |     | 0     |               |      |      | 1   |        |    |      | 0     |      |      |    | 1   |          |     |       | 0    |      |     |     | 1   | 0    |

| Name     |       |   |            |   |              |                        |   |      | SYN    |       |      |     |       |               |      |      | SYN |        |    |      |       |      |      |    | SYN | //       |     |       |      |      |     |     | SYN |      |

| * 14/ 11 |       |   |            |   |              |                        |   |      |        | - 144 |      |     |       |               |      |      |     |        |    |      |       |      |      |    |     |          |     |       |      |      |     |     |     |      |

<sup>\*</sup> Word length

Word length 1: 4-bit gradation data specification

| VV | JIU  | IE  | Hy                  | uп   | 1. ' | 4-L | иų  | ji a | ua          | liO | II U | ald | <u> </u> | μe            | CIII | Ca       | liUi       | 1           |     |     |     |              |     |      |

|----|------|-----|---------------------|------|------|-----|-----|------|-------------|-----|------|-----|----------|---------------|------|----------|------------|-------------|-----|-----|-----|--------------|-----|------|

| 9  | 10   | 11  | 12                  | 13   | 14   | 15  | 16  | 17   | 18          | 19  | 20   | 21  | 22       | 23            | 24   | 393      | 394        | 395         | 396 | 397 | 398 | 399          | 400 |      |

|    |      |     |                     |      |      |     |     |      |             |     |      |     |          |               |      |          |            |             |     |     |     |              | П   | L    |

| f  | 5    | ſ   | ſ                   | f    | ſ    | ſ   | 4   | £    | Ъ           | 1   | ſ    | f   | Ъ        | 1             | ſ    | W        | f          | ſ           | ſ   | ſ   | £   | f            | ſ   |      |

| 1  |      |     |                     |      |      |     |     |      |             |     |      |     |          |               |      | //:      |            |             |     |     |     |              |     | 1    |

| *  |      | Res | sisto               | or a | ddr  | ess |     |      | data (0) da |     |      |     |          | latic<br>a (1 |      |          | ata<br>ata |             |     |     |     | latic<br>(95 |     | STOP |

| F  | Resi |     | r <b>se</b><br>g_da |      |      | dat | а   | li   |             |     |      |     |          | _dat<br>:0]   | 1    | li.      | ght_<br>[3 | dat:<br>:0] | 94  | li. |     | dat:<br>:0]  | 95  | 3101 |

|    |      |     | 0                   |      |      |     | 1   |      | 0           |     |      |     |          |               | 1    | <b>I</b> |            |             | 0   |     |     |              | 1   | 0    |

|    |      |     |                     |      |      |     | SYN |      |             |     |      |     |          |               | SYN  | //       |            |             |     |     |     |              | SYN |      |

#### (4) I2C-compliant serial communication method (I2C mode)

Word length 0: 8-bit gradation data specification

| bit<br>SCL |        | 1 2 3 4 5 6 7 8<br>f f f f f f f      | 9      | 10 11 12 13 14 15 16 17                 | 18<br><b>f</b> | 19 20 21 22 23 24 25 26 f f f f f f f | V          | 874 875 876 877 878 879 880 881<br><b>f f f f f f</b> | 882  |        |

|------------|--------|---------------------------------------|--------|-----------------------------------------|----------------|---------------------------------------|------------|-------------------------------------------------------|------|--------|

| SDA        | $\Box$ | 0 1 0                                 | 1      | 0                                       | 1              |                                       | 1)         |                                                       | 1    |        |

| Name       | START  | Device Device R address W             | (Open) | * Resistor address                      | en)            | Gradation data (0)                    | (Operation | Gradation data (95)                                   | pen) | STOP   |

| Ivanic     | SIAKI  | Device selection data<br>dvc_dat[7:0] | dO)    | Resistor selection data<br>reg_dat[7:0] | dO)            | light_dat0[7:0]                       | (Ö         | light_dat95[7:0]                                      | o)   | 3101   |

| SDO        | 0      | 0                                     | 1      | 0                                       | 1              | 0                                     | 1//        | 0                                                     | 1    | 0      |

| Name       | (Open) | (Open)                                | ACK    | (Open)                                  | ACK            | (Open)                                | ΑĊ         | (Open)                                                | ACK  | (Open) |

<sup>\*</sup> Word length

| VVC | ord length 1: 4-bit (                | gra  | dation data         | a specificat        | 101          | n                                          |                      |      |        |

|-----|--------------------------------------|------|---------------------|---------------------|--------------|--------------------------------------------|----------------------|------|--------|

| 10  | 11 12 13 14 15 16 17                 | 18   | 19 20 21 22         | 23 24 25 26         | $\mathbb{N}$ | 442 443 444 445                            | 446 447 448 449      | 450  |        |

| ſ   |                                      | ſ    | THH                 |                     | Ŋ            | $\mathbf{T}\mathbf{T}\mathbf{T}\mathbf{T}$ | T                    | ſ    |        |

| 1   |                                      | 1    |                     |                     | 1            |                                            |                      | 1    |        |

| *   | Resistor address                     | pen) | Gradation data (0)  | Gradation data (1)  |              | Gradation data (94)                        | Gradation data (95)  | pen) | STOP   |

|     | Resistor selection data reg_dat[7:0] | 0)   | light_dat0<br>[3:0] | light_dat1<br>[3:0] | Ö,           | light_dat94<br>[3:0]                       | light_dat95<br>[3:0] | dO)  | 3101   |

|     | 0                                    | 1    | (                   | )                   | 1//          |                                            | 0                    | 1    | 0      |

|     | (Open)                               | ACK  | (Op                 | oen)                | Αď           | (Op                                        | en)                  | ACK  | (Open) |

<sup>\*</sup> Word length

<sup>\*</sup> Word length

<sup>\*</sup> Word length

The names and communication formats of each communication method are shown below.

| Communication mode name                            | Abbreviation start signal | Start signal           | Stop signal            | Separator              | Data<br>width | Response      |

|----------------------------------------------------|---------------------------|------------------------|------------------------|------------------------|---------------|---------------|

| Addressed serial communication method (SP-D8 mode) | SP-D8                     | "1 1111 1111 0"        | "1 1111 1111"          | 0: Continue<br>1: End  | 8             | ACK<br>(NACK) |

| Addressed serial communication method (SP-D7 mode) | SP-D7                     | "1111 1111 0"          | "1111 1111"            | 0: Continue<br>1: End  | 7             | ACK<br>(NACK) |

| Addressed serial communication method (CE-D8 mode) | CE-D8                     | CE falling edge        | CE rising edge         | (None)                 | 8             | SYN           |

| I2C-compliant serial communication (I2C mode)      | I2C                       | I2C standard compliant | I2C standard compliant | I2C standard compliant | 8             | ACK<br>(NACK) |

[Start signal] Regardless of whether in standby or in communication, communication is initialized and the device is

placed in a state waiting for device selection data.

[Stop signal] Terminates communication and enters a start signal waiting state.

With SP-D8/SP-D7, the communication termination procedure (sending "1" to the separator / sending

stop signal) can be omitted by sending the start signal after sending the gradation data.

[Separator] A bit to be inserted between transmitted data.

With SP-D8/SP-D7, sending "1" to the separator terminates communication and enters the state of

waiting for a stop signal or start signal.

With I2C, the separator is assigned to the ACK response.

[Data width] Transmission data bit width.

With SP-D7, the data that can be specified is limited (no word length specification, 128 gradation

specification).

[Response] Response type. At the falling edge of the SCL signal, this IC outputs data to the SDO terminal.

With SP-D8/SP-D7/I2C, the received data is checked and the result is returned (ACK or NACK). With CE-D8, a synchronous signal is output to indicate that communication is in progress (SYN).

The received data is not checked.

The command structure is shown below.

#### [Device specification]

Received data is captured when the device ID and device address match the IC settings. The device ID is fixed as "010". The same command can be sent to all devices by specifying "1111" as the device address. The correspondence between device addresses and device address terminals is shown in the table below.

|                    |   | De        | vice sele | ection da | ita dvc_c | lat[7:0] |                 |    |

|--------------------|---|-----------|-----------|-----------|-----------|----------|-----------------|----|

| Communication mode | 7 | 6         | 5         | 4         | 3         | 2        | 1               | 0  |

| mode               |   | Device II | )         |           | Device    | address  |                 | RW |

| Standard           | 0 | 1         | 0         | ADD:      | 1[1.0]    | ADR      | η[1. <b>η</b> ] | 0  |

| SP-D7              | U | 1         | ¦ '       | ADK.      | [[1.0]    | ADN      | J[1.U]          | _  |

#### [Resistor specification]

| Communication |   |   | [ | Devi | ce s | elec | tion | data | reg   | d <u>a</u> 1 | :[7:0 | )] |   |   |   |

|---------------|---|---|---|------|------|------|------|------|-------|--------------|-------|----|---|---|---|

| mode          | 7 | Ţ | 6 | T    | 5    | Ţ    | 4    | T    | 3     | Т            | 2     | Ţ  | 1 | T | 0 |

| Standard      | * |   |   |      |      |      | _    |      | 4     | -l -l -      |       |    |   |   |   |

| SP-D7         | _ |   |   |      |      |      | R    | esis | tor a | aare         | ess   |    |   |   |   |

\* Word length

Word length Specify the data unit for gradation data.

| Word length<br>specification | Word length |

|------------------------------|-------------|

| "0"                          | 8bit        |

| "1"                          | 4bit        |

Register address (lighting position specification)

Specify the address of the gradation register. The

upper limit of addresses that can be specified and

the number of gradation data that can be continuously

transferred vary depending on the division mode

setting and word length specification (Table 6).

3. Resistor address (special address)

By specifying 0x7F (127), all gradation registers can be specified in one batch.

By specifying 0x78 (120), the power-saving data register can be specified.

#### [Gradation data]

| Communication     |   | Devi           | ce select | ion data  | light_da | t[7:0]   |         |    |  |  |  |  |  |

|-------------------|---|----------------|-----------|-----------|----------|----------|---------|----|--|--|--|--|--|

| mode              | 7 | 6              | 5         | 4         | 3        | 2        | 1       | 0  |  |  |  |  |  |

| Standard (8 bits) |   | Gradation data |           |           |          |          |         |    |  |  |  |  |  |

| Standard (4 bits) |   | Gradatio       | on data N | 1         | G        | radation | data N+ | -1 |  |  |  |  |  |

| SP-D7             |   |                | Gra       | adation c | lata     |          |         | _  |  |  |  |  |  |

1. Gradation specification Specify the gradation data in one of the following formats: 8-bit (256 gradations), 7-bit (128 gradations), or 4-bit (16 gradations). (Table 7)

Power-saving mode

When specifying the

power-saving data

register in the register

address, the lower

4 bits are treated as

power-saving data.

| Power-saving data | Output current or output duty cycle |  |  |  |  |

|-------------------|-------------------------------------|--|--|--|--|

| "00"              | 100 %                               |  |  |  |  |

| "01"              | 75 %                                |  |  |  |  |

| "10"              | 50 %                                |  |  |  |  |

| "11"              | 25 %                                |  |  |  |  |

| Communication | Device selection data light_dat[7:0] |   |   |   |                                     |   |            |                  |

|---------------|--------------------------------------|---|---|---|-------------------------------------|---|------------|------------------|

| mode          | 7                                    | 6 | 5 | 4 | 3                                   | 2 | 1          | 0                |

| Standard      | 0                                    | 0 | 0 | 0 | Power-saving data (current control) |   |            |                  |

| SP-D7         | _                                    | 0 | 0 | 0 |                                     |   | (duty cycl | y cycle control) |

Table 6: Register address and lighting position

| Destates               | Matrix configuration                            |                    |                    |              |                    |  |  |

|------------------------|-------------------------------------------------|--------------------|--------------------|--------------|--------------------|--|--|

| Resistor               | $24\times1$ $24\times2$ $24\times4$ $16\times8$ |                    |                    |              |                    |  |  |

| address                | 24 ^ 1                                          | 24 ^ 2             | 24 ^ 4             | Even columns | Odd columns        |  |  |

| 0x00 (0)               | (0, 0)                                          | (0, 0)             | (0, 0)             | (0, 0)       | (1, 0)             |  |  |

| 0x01 (1)               | (1, 0)                                          | (1, 0)             | (1, 0)             | (2, 0)       | (3, 0)             |  |  |

| 0x02 (2)               | (2, 0)                                          | (2, 0)             | (2, 0)             | (4, 0)       | (5, 0)             |  |  |

| 0x03 (3)               | (3, 0)                                          | (3, 0)             | (3, 0)             | (6, 0)       | (7, 0)             |  |  |

| 0x04 (4)               | (4, 0)                                          | (4, 0)             | (4, 0)             | (8, 0)       | (9, 0)             |  |  |

| 0x05 (5)               | (5, 0)                                          | (5, 0)             | (5, 0)             | (10, 0)      | (11, 0)            |  |  |

| 0x06 (6)               | (6, 0)                                          | (6, 0)             | (6, 0)             | (12, 0)      | (13, 0)            |  |  |

| 0x07 (7)               | (7, 0)                                          | (7, 0)             | (7, 0)             | (14, 0)      | (15, 0)            |  |  |

| 0x08 (8)               | (8, 0)                                          | (8, 0)             | (8, 0)             | (0, 1)       | (1, 1)             |  |  |

| 0x09 (9)               | (9, 0)                                          | (9, 0)             | (9, 0)             | (2, 1)       | (3, 1)             |  |  |

| 0x0A (10)              | (10, 0)                                         | (10, 0)            | (10, 0)            | (4, 1)       | (5, 1)             |  |  |

| 0x0B (11)              | (11, 0)                                         | (11, 0)            | (11, 0)            | (6, 1)       | (7, 1)             |  |  |

| 0x0C (12)              | (12, 0)                                         | (12, 0)            | (12, 0)            | (8, 1)       | (9, 1)             |  |  |

| 0x0D (13)              | (13, 0)                                         | (13, 0)            | (13, 0)            | (10, 1)      | (11, 1)            |  |  |

| 0x0E (14)<br>0x0F (15) | (14, 0)<br>(15, 0)                              | (14, 0)<br>(15, 0) | (14, 0)<br>(15, 0) | (12, 1)      | (13, 1)<br>(15, 1) |  |  |

| 0x10 (16)              | (16, 0)                                         | (16, 0)            | (16, 0)            | (0, 2)       | (15, 1) $(1, 2)$   |  |  |

| 0x10 (10)<br>0x11 (17) | (17, 0)                                         | (17, 0)            | (17, 0)            | (2, 2)       | (3, 2)             |  |  |

| 0x11 (17)<br>0x12 (18) | (18, 0)                                         | (18, 0)            | (18, 0)            | (4, 2)       | (5, 2)             |  |  |

| 0x13 (19)              | (19, 0)                                         | (19, 0)            | (19, 0)            | (6, 2)       | (7, 2)             |  |  |

| 0x14 (20)              | (20, 0)                                         | (20, 0)            | (20, 0)            | (8, 2)       | (9, 2)             |  |  |

| 0x15 (21)              | (21, 0)                                         | (21, 0)            | (21, 0)            | (10, 2)      | (11, 2)            |  |  |

| 0x16 (22)              | (22, 0)                                         | (22, 0)            | (22, 0)            | (12, 2)      | (13, 2)            |  |  |

| 0x17 (23)              | (23, 0)                                         | (23, 0)            | (23, 0)            | (14, 2)      | (15, 2)            |  |  |

| 0x18 (24)              | _                                               | (0, 1)             | (0, 1)             | (0, 3)       | (1, 3)             |  |  |

| 0x19 (25)              | _                                               | (1, 1)             | (1, 1)             | (2, 3)       | (3, 3)             |  |  |

| 0x1A (26)              | -                                               | (2, 1)             | (2, 1)             | (4, 3)       | (5, 3)             |  |  |

| 0x1B (27)              | _                                               | (3, 1)             | (3, 1)             | (6, 3)       | (7, 3)             |  |  |

| 0x1C (28)              | _                                               | (4, 1)             | (4, 1)             | (8, 3)       | (9, 3)             |  |  |

| 0x1D (29)              | _                                               | (5, 1)             | (5, 1)             | (10, 3)      | (11, 3)            |  |  |

| 0x1E (30)              | _                                               | (6, 1)             | (6, 1)             | (12, 3)      | (13, 3)            |  |  |

| 0x1F (31)              | _                                               | (7, 1)             | (7, 1)             | (14, 3)      | (15, 3)            |  |  |

| 0x20 (32)              |                                                 | (8, 1)             | (8, 1)             | (0, 4)       | (1, 4)             |  |  |

| 0x21 (33)              | _                                               | (9, 1)             | (9, 1)             | (2, 4)       | (3, 4)             |  |  |

| 0x22 (34)              |                                                 | (10, 1)            | (10, 1)            | (4, 4)       | (5, 4)             |  |  |

| 0x23 (35)<br>0x24 (36) | _                                               | (11, 1)            | (11, 1)<br>(12, 1) | (6, 4)       | (7, 4)<br>(9, 4)   |  |  |

| 0x24 (30)<br>0x25 (37) |                                                 | (13, 1)            | (13, 1)            | (10, 4)      | (11, 4)            |  |  |

| 0x26 (38)              |                                                 | (14, 1)            | (14, 1)            | (12, 4)      | (13, 4)            |  |  |

| 0x27 (39)              |                                                 | (15, 1)            | (15, 1)            | (14, 4)      | (15, 4)            |  |  |

| 0x28 (40)              | _                                               | (16, 1)            | (16, 1)            | (0, 5)       | (1, 5)             |  |  |

| 0x29 (41)              | _                                               | (17, 1)            | (17, 1)            | (2, 5)       | (3, 5)             |  |  |

| 0x2A (42)              | _                                               | (18, 1)            | (18, 1)            | (4, 5)       | (5, 5)             |  |  |

| 0x2B (43)              | _                                               | (19, 1)            | (19, 1)            | (6, 5)       | (7, 5)             |  |  |

| 0x2C (44)              | _                                               | (20, 1)            | (20, 1)            | (8, 5)       | (9, 5)             |  |  |

| 0x2D (45)              | _                                               | (21, 1)            | (21, 1)            | (10, 5)      | (11, 5)            |  |  |

| 0x2E (46)              | _                                               | (22, 1)            | (22, 1)            | (12, 5)      | (13, 5)            |  |  |

| 0x2F (47)              | _                                               | (23, 1)            | (23, 1)            | (14, 5)      | (15, 5)            |  |  |

| Destates  | Matrix configuration |        |         |              |             |  |  |

|-----------|----------------------|--------|---------|--------------|-------------|--|--|

| Resistor  | 94 ∨ 1               | 24×2   | 24×4    | 16×8         |             |  |  |

| address   | $24 \times 1$        | 24 × 2 | 24 × 4  | Even columns | Odd columns |  |  |

| 0x30 (48) | _                    | _      | (0, 2)  | (0, 6)       | (1, 6)      |  |  |

| 0x31 (49) | _                    | _      | (1, 2)  | (2, 6)       | (3, 6)      |  |  |

| 0x32 (50) | 1                    | -      | (2, 2)  | (4, 6)       | (5, 6)      |  |  |

| 0x33 (51) | _                    | _      | (3, 2)  | (6, 6)       | (7, 6)      |  |  |

| 0x34 (52) | -                    | -      | (4, 2)  | (8, 6)       | (9, 6)      |  |  |

| 0x35 (53) | -                    | 1      | (5, 2)  | (10, 6)      | (11, 6)     |  |  |

| 0x36 (54) | _                    |        | (6, 2)  | (12, 6)      | (13, 6)     |  |  |

| 0x37 (55) | _                    | _      | (7, 2)  | (14, 6)      | (15, 6)     |  |  |

| 0x38 (56) | _                    | _      | (8, 2)  | (0, 7)       | (1, 7)      |  |  |

| 0x39 (57) | _                    | _      | (9, 2)  | (2, 7)       | (3, 7)      |  |  |

| 0x3A (58) | _                    | _      | (10, 2) | (4, 7)       | (5, 7)      |  |  |

| 0x3B (59) | _                    |        | (11, 2) | (6, 7)       | (7, 7)      |  |  |

| 0x3C (60) | _                    |        | (12, 2) | (8, 7)       | (9, 7)      |  |  |

| 0x3D (61) | _                    | _      | (13, 2) | (10, 7)      | (11, 7)     |  |  |

| 0x3E (62) | _                    | _      | (14, 2) | (12, 7)      | (13, 7)     |  |  |

| 0x3F (63) | _                    | _      | (15, 2) | (14, 7)      | (15, 7)     |  |  |

| 0x40 (64) |                      |        | (16, 2) | _            | _           |  |  |

| 0x41 (65) | _                    | _      | (17, 2) | _            | _           |  |  |

| 0x42 (66) | _                    | _      | (18, 2) | _            | _           |  |  |

| 0x43 (67) |                      | _      | (19, 2) | _            | _           |  |  |

| 0x44 (68) | -                    | 1      | (20, 2) | -            | _           |  |  |

| 0x45 (69) | _                    | _      | (21, 2) | _            | _           |  |  |

| 0x46 (70) | _                    | _      | (22, 2) | -            | _           |  |  |

| 0x47 (71) | _                    | _      | (23, 2) | _            | _           |  |  |

| 0x48 (72) | _                    | _      | (0, 3)  | _            | _           |  |  |

| 0x49 (73) |                      |        | (1, 3)  | _            |             |  |  |

| 0x4A (74) | _                    | _      | (2, 3)  | _            | _           |  |  |

| 0x4B (75) | _                    | _      | (3, 3)  | _            | _           |  |  |

| 0x4C (76) |                      | _      | (4, 3)  | _            |             |  |  |

| 0x4D (77) |                      |        | (5, 3)  |              |             |  |  |

| 0x4E (78) | _                    |        | (6, 3)  | _            | _           |  |  |

| 0x4F (79) |                      |        | (7, 3)  |              | _           |  |  |

| 0x50 (80) |                      | _      | (8, 3)  |              |             |  |  |

| 0x51 (81) | _                    | _      | (9, 3)  | _            | _           |  |  |

| 0x52 (82) | _                    |        | (10, 3) | _            |             |  |  |

| 0x53 (83) | _                    |        | (11, 3) | _            |             |  |  |

| 0x54 (84) |                      |        | (12, 3) | _            |             |  |  |

| 0x55 (85) |                      | _      | (13, 3) | _            |             |  |  |

| 0x56 (86) |                      |        | (14, 3) | _            |             |  |  |

| 0x57 (87) | _                    | _      | (15, 3) | _            | _           |  |  |

| 0x58 (88) |                      |        | (16, 3) | _            |             |  |  |

| 0x59 (89) |                      | -      | (17, 3) | _            |             |  |  |

| 0x5A (90) |                      |        | (18, 3) | _            |             |  |  |

| 0x5B (91) |                      |        | (19, 3) | _            | _           |  |  |

| 0x5C (92) |                      |        | (20, 3) | _            | _           |  |  |

| 0x5D (93) |                      |        | (21, 3) | _            |             |  |  |

| 0x5E (94) |                      |        | (22, 3) | _            | _           |  |  |

| 0x5F (95) | _                    | _      | (23, 3) | _            | _           |  |  |

Table 7: Lighting gradation and output duty cycle

| Lighting<br>gradation<br>(8 bit)<br>*Represen- | Lighting<br>gradation<br>(7 bit)<br>*Represen- | Lighting gradation (4 bit) |               | Matrix cor    | nfiguration   |             |

|------------------------------------------------|------------------------------------------------|----------------------------|---------------|---------------|---------------|-------------|

| tative value                                   | tative value                                   | ` ′                        | $24 \times 1$ | $24 \times 2$ | $24 \times 4$ | 16×8        |

| 0                                              | 0                                              | 0                          | (Light off)   | (Light off)   | (Light off)   | (Light off) |

| 15                                             | 7                                              | ı                          | 0.37 %        | 0.18 %        | 0.09 %        | 0.05 %      |

| 31                                             | 15                                             | 1                          | 0.76 %        | 0.38 %        | 0.19 %        | 0.09 %      |

| 47                                             | 23                                             | 2                          | 1.15 %        | 0.57 %        | 0.29 %        | 0.14 %      |

| 63                                             | 31                                             | 3                          | 1.54 %        | 0.77 %        | 0.38 %        | 0.19 %      |

| 79                                             | 39                                             | 4                          | 2.29 %        | 1.15 %        | 0.57 %        | 0.29 %      |

| 95                                             | 47                                             | 5                          | 3.08 %        | 1.54 %        | 0.77 %        | 0.38 %      |

| 111                                            | 55                                             | 6                          | 4.59 %        | 2.29 %        | 1.15 %        | 0.57 %      |

| 127                                            | 63                                             | 7                          | 6.15 %        | 3.08 %        | 1.54 %        | 0.77 %      |

| 143                                            | 71                                             | 8                          | 9.18 %        | 4.59 %        | 2.29 %        | 1.15 %      |

| 159                                            | 79                                             | 9                          | 12.30 %       | 6.15 %        | 3.08 %        | 1.54 %      |

| 175                                            | 87                                             | 10                         | 18.36 %       | 9.18 %        | 4.59 %        | 2.29 %      |

| 191                                            | 95                                             | 11                         | 24.61 %       | 12.30 %       | 6.15 %        | 3.08 %      |

| 207                                            | 103                                            | 12                         | 36.72 %       | 18.36 %       | 9.18 %        | 4.59 %      |

| 223                                            | 111                                            | 13                         | 49.22 %       | 24.61 %       | 12.30 %       | 6.15 %      |

| 239                                            | 119                                            | 14                         | 73.44 %       | 36.72 %       | 18.36 %       | 9.18 %      |

| 255                                            | 127                                            | 15                         | 98.44 %       | 49.22 %       | 24.61 %       | 12.30 %     |

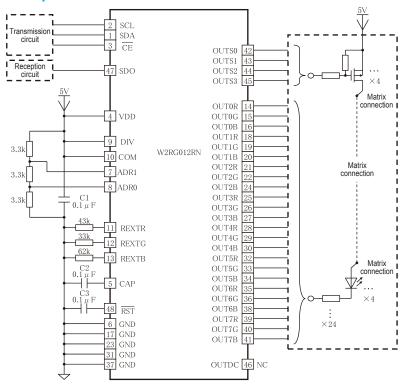

# Application Circuit Example

[Setting example]

DIV: 24 x 4 configuration, COM: I2C communication, ADR: device address "1101", constant current setting R: 59.5 mA (14.9 mA), G: 77.6 mA (19.4 mA), B: 41.3 mA (10.3 mA)

(Values in parentheses are effective values)

#### Precautions for Use

- (1) Check the operation at your communication frequency before use.

- (2) Each input circuit should be determined with due consideration of the voltage, chattering, and static electricity of the input to be connected.

- (3) An electrostatic discharge (ESD) protection circuit is built in, but If static electricity exceeding its function is applied, it may be destroyed. When handling, take sufficient precautions such as grounding your body.

- (4) Consider allowable losses under actual operating conditions and perform thermal design with sufficient margins. When the voltage loaded onto the IC is high, such as when the number of LEDs driven in series is small, heat generation in the IC can be reduced by inserting a resistor to distribute power consumption.

- (5) This IC has a built-in thermal shutdown circuit. When the chip temperature becomes abnormally high, this circuit operates, the output terminal becomes open, and the chip temperature returns to the normal range. Do not use this circuit as a regular function, as it is an emergency protection function.

Please check each region's Terms & Conditions by region website.

# **OMRON AMUSEMENT Co., Ltd**

#### **Regional Contact**

Americas Europe

https://components.omron.com/us-en/ https://components.omron.com/eu-en/

Asia-Pacific China

https://components.omron.com/sg-en/ https://components.omron.com.cn/

Korea Japa

https://components.omron.com/kr-en/ https://components.omron.com/jp-ja/